AI 기술이 빠르게 발전하면서 반도체에 요구되는 성능도 함께 치솟고 있어요. 더 빠른 연산 속도와 더 대규모의 데이터 처리 능력이 요구되는 가운데, 예상치 못한 구조적 한계가 수면 위로 떠올랐답니다.

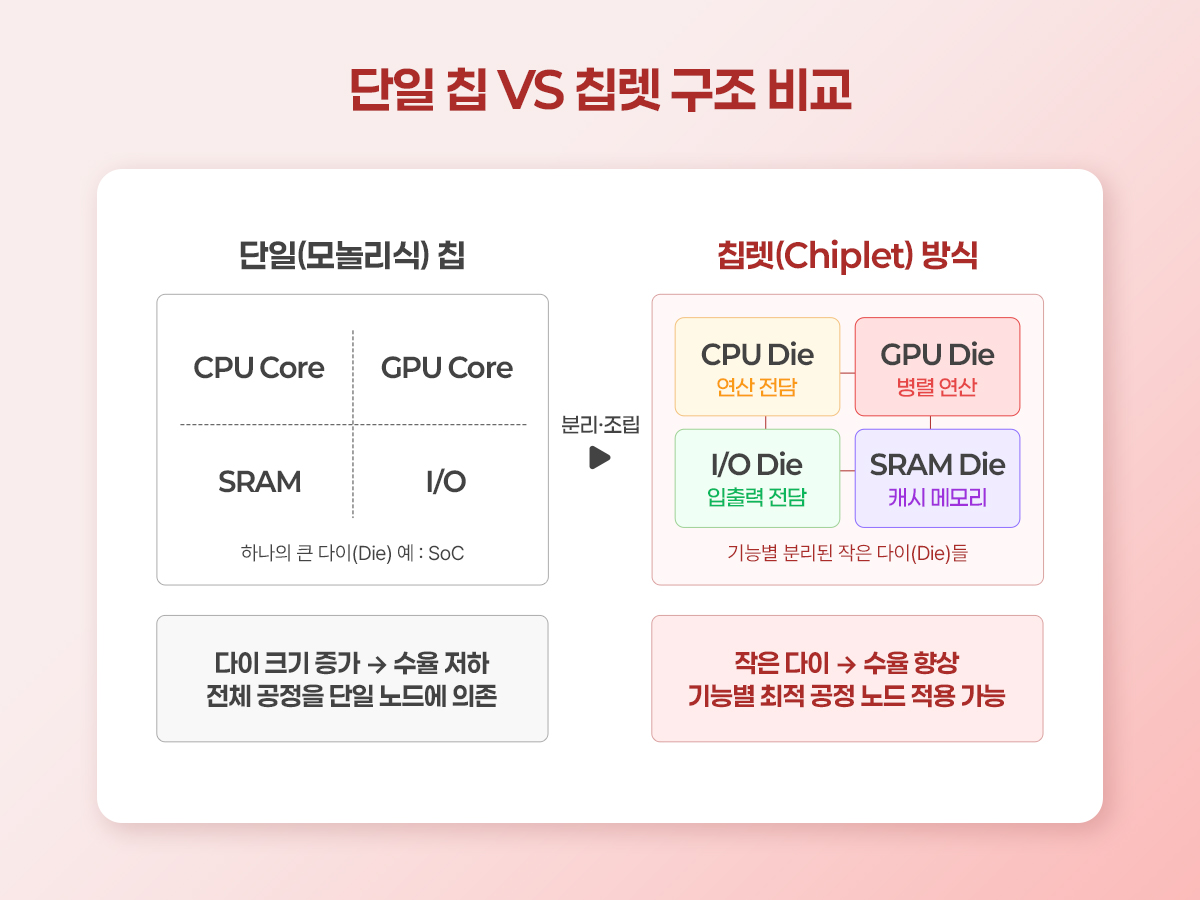

칩을 더 크게, 더 복잡하게 만들수록 오히려 수율은 떨어지고 비용은 올라가는 딜레마였어요. 공정이 미세해질수록 한계는 더욱 뚜렷해졌고, AI 반도체처럼 CPU·GPU·메모리를 한 칩에 모두 담으려 할수록 설계 복잡도와 비용 부담도 함께 커졌죠.

이 구조적 한계를 돌파하기 위해 등장한 것이 바로 ‘칩렛(Chiplet)’이에요. 하나의 거대한 칩을 무리하게 구현하는 대신, 기능별로 최적화된 작은 칩들을 조합해 하나의 시스템처럼 동작시키는 새로운 설계 방식이죠. [반도체의 모든 것]에서 칩렛이 무엇인지, 왜 지금 반도체 업계의 핵심 트렌드로 주목받는지 차근차근 풀어드릴게요!

📌한눈에 보는 칩렛(Chiplet)

| 1️⃣정의:하나의 반도체를 기능별로 나누어 제작한 뒤, 하나처럼 동작하게 연결하는 기술 2️⃣핵심 장점: 수율 개선 + 비용 절감 + 모듈별 독립 업그레이드 3️⃣특징:단일 SoC의 한계를 극복하는 ‘모듈형 설계’ 패러다임 |

▪칩렛(Chiplet)

: 하나의 큰 반도체 칩을 기능별 작은 단위(다이)로 나누어 각각 제조한 뒤,

하나의 패키지 안에서 연결해 완성된 시스템처럼 동작하게 만드는 반도체 설계·패키징 방식

조금 더 쉽게 말하면, 기존에는 CPU·GPU·메모리·I/O 등 모든 기능을 하나의 큰 다이 안에 몰아넣는 단일 칩(모놀리식) 방식이었다면,

칩렛은 이 기능들을 잘게 쪼개 각각 따로 만든 뒤 다시 하나의 패키지로 조립하는 방식이에요.

마치 레고 블록처럼, 필요한 조각을 골라 붙여 완성하는 개념이죠.

▪왜 칩렛이 필요하게 됐을까?

단일 SoC 방식이 한계에 부딪힌 데는 세 가지 이유가 있어요.

① 최신 공정 웨이퍼의 높은 가격

초미세 공정의 성능 향상 폭은 점점 줄어드는 반면, 생산 비용은 몇 배로 치솟고 있어요.

3nm, 2nm 같은 최신 공정일수록 웨이퍼 가격이 큰 폭으로 올라, 단일 SoC 방식으로는 비용 부담이 갈수록 커질 수밖에 없어요.

② 면적이 커질수록 수율이 낮아짐

웨이퍼 한 장에서 결함이 50개 발생할 때, 큰 칩 100개를 생산하면 수율은 50%에 불과하지만, 작은 칩 1,000개를 생산하면 수율이 95%까지 올라가요. 칩이 커질수록 결함 하나가 제품 전체를 불량으로 만들 확률이 높아지기 때문에, ‘완벽한 하나’를 만들기가 점점 어려워지는 구조예요.

③ 기능별 최적 공정 적용의 필요성

고성능이 요구되는 CPU 연산 코어는 최신 3nm 공정이 유리하지만, 상대적으로 공정 노드에 덜 민감한 SRAM이나 아날로그 회로는 기존 7nm 공정을 적용해도 충분해요. I/O처럼 안정성과 신뢰성이 중요한 기능은 오히려 검증된 구형 공정이 더 적합한 경우도 많아요. 단일 SoC는 이 모든 기능을 하나의 공정으로 묶어야 하니, 비쌀 필요 없는 부분에도 최첨단 비용을 지불하는 구조였던 거예요.

| ➕단일 SoC의 한계 3가지 – 최신 공정 웨이퍼 가격 급등 ⠀⠀:3nm·2nm 등 최신 공정의 웨이퍼 제조 비용 상승으로 단일 SoC 방식의 비용 부담 가중 – 수율 저하 ⠀⠀: 칩 면적이 클수록 불량률 급증 → ‘완벽한 하나’를 만들기 어려운 구조적 한계 – 기능별 최적 공정 상이 ⠀⠀: CPU는 최신 공정, I/O는 구형 공정이 유리 → 단일 공정 강제 적용의 비효율 |

칩렛의 등장 배경을 살펴봤다면, 이번엔 칩렛이 실제로 어떤 구조적 특징을 갖고 있는지 조금 더 깊이 들여다볼게요.

① 기능별 독립 분리 구조

칩렛은 각각의 조각이 단독으로는 동작할 수 없어요. 연산을 담당하는 CPU Die와 외부 입출력을 담당하는 I/O Die가 물리적으로 분리되어 있고, 반드시 함께 통합되어야 하나의 완전한 프로세서로 동작해요. 각 칩렛이 맡은 역할만 전담하고, 서로 연결되어야 비로소 하나의 시스템이 완성되는 구조랍니다.

② 기능별 이종(異種) 공정 노드 적용

각 칩렛은 서로 다른 프로세스 노드를 사용하여 제조될 수 있으며, GaN 및 Si 칩렛과 같은 여러 재료를 동일한 패키지에 결합하는 것도 가능해요. 기능에 따라 가장 적합한 공정과 소재를 각각 선택할 수 있다는 점이 단일 SoC와의 핵심적인 차이랍니다.

③ 칩렛 간 표준 인터페이스의 필요성

칩렛은 GPU, CPU, 메모리, 전력 및 통제제어장치 등을 필요에 따라 결합하면 되기 때문에 빠른 설계와 제작이 가능해요. 하지만 여러 개의 칩을 집적하기 때문에 설계가 복잡하다는 단점도 있어요. 이 때문에 서로 다른 제조사의 칩렛이 원활하게 연결될 수 있도록 업계 공통 표준 인터페이스의 필요성이 함께 대두되고 있어요.

| ➕칩렛의 구조적 특징 3가지 – 기능별 독립 분리 구조 ⠀⠀: 각 칩렛은 단독 동작 불가 → CPU Die·I/O Die 등이 각자 역할 전담 후 통합 – 기능별 이종 공정 노드 적용 ⠀⠀: 기능마다 최적 공정·소재 선택 가능 → GaN·Si 등 이종 재료의 동일 패키지 결합도 가능 – 표준 인터페이스의 필요성 ⠀⠀: 빠른 설계·제작의 장점과 함께, 복잡한 설계 및 칩렛 간 호환 표준 확보가 과제 |

단일 SoC의 한계를 넘기 위해 등장한 칩렛, 그렇다면 칩렛이 실제로 가져다주는 이점은 무엇일까요? 크게 세 가지로 정리할 수 있어요.

① 수율 개선

앞서 살펴봤듯 칩이 커질수록 수율은 급격히 낮아져요. 칩 사이즈가 커짐에 따라 수율이 매우 빠르게 감소하며, 칩렛 방식 대비 단일(모놀리식) 칩 생산 방식에서 수율 하락 폭이 훨씬 크게 나타나요. 칩렛은 기능별로 작은 다이를 따로 만들기 때문에 각 조각의 불량률을 낮게 유지할 수 있고, 결함이 생기더라도 해당 칩렛만 교체하면 되니 전체 손실을 최소화할 수 있어요.

② 비용 절감

칩렛은 일반적으로 원형 웨이퍼에서 더 작은 면적으로 제조되므로 제조 결함의 영향이 감소하고 면적 활용도가 증가해요. 결과적으로 웨이퍼 수율이 크게 높아지기 때문에 비용 절감으로 이어져요. 또한 기능별로 최적의 공정 노드를 선택할 수 있어, 굳이 비싼 최신 공정을 전체에 적용할 필요가 없어 제조 원가를 추가로 낮출 수 있어요.

③ 모듈별 독립 업그레이드

시스템에 업데이트가 필요한 경우 패키징 내의 한 칩렛만 다른 것으로 교체할 수 있어요. 이는 전체 단일 구성 요소를 재설계하는 것보다 훨씬 적은 작업이며, 일부를 재설계하더라도 단일 반도체 패키지에서 발생할 새로운 검증 비용이 생기지 않아요. 필요한 부분만 골라 업그레이드할 수 있다는 점은 빠르게 변화하는 AI 반도체 시장에서 특히 강력한 장점이에요.

| ➕ 칩렛의 장점 3가지 핵심 포인트 – 수율 개선 ⠀⠀: 작은 다이 단위 생산으로 불량률 최소화 → 단일 칩 대비 수율 하락 폭 대폭 축소 – 비용 절감 ⠀⠀: 웨이퍼 면적 활용도 향상 + 기능별 최적 공정 선택 → 제조 원가 절감 – 모듈별 독립 업그레이드 ⠀⠀: 필요한 칩렛만 교체·업그레이드 가능 → 재설계 및 검증 비용 미발생 |

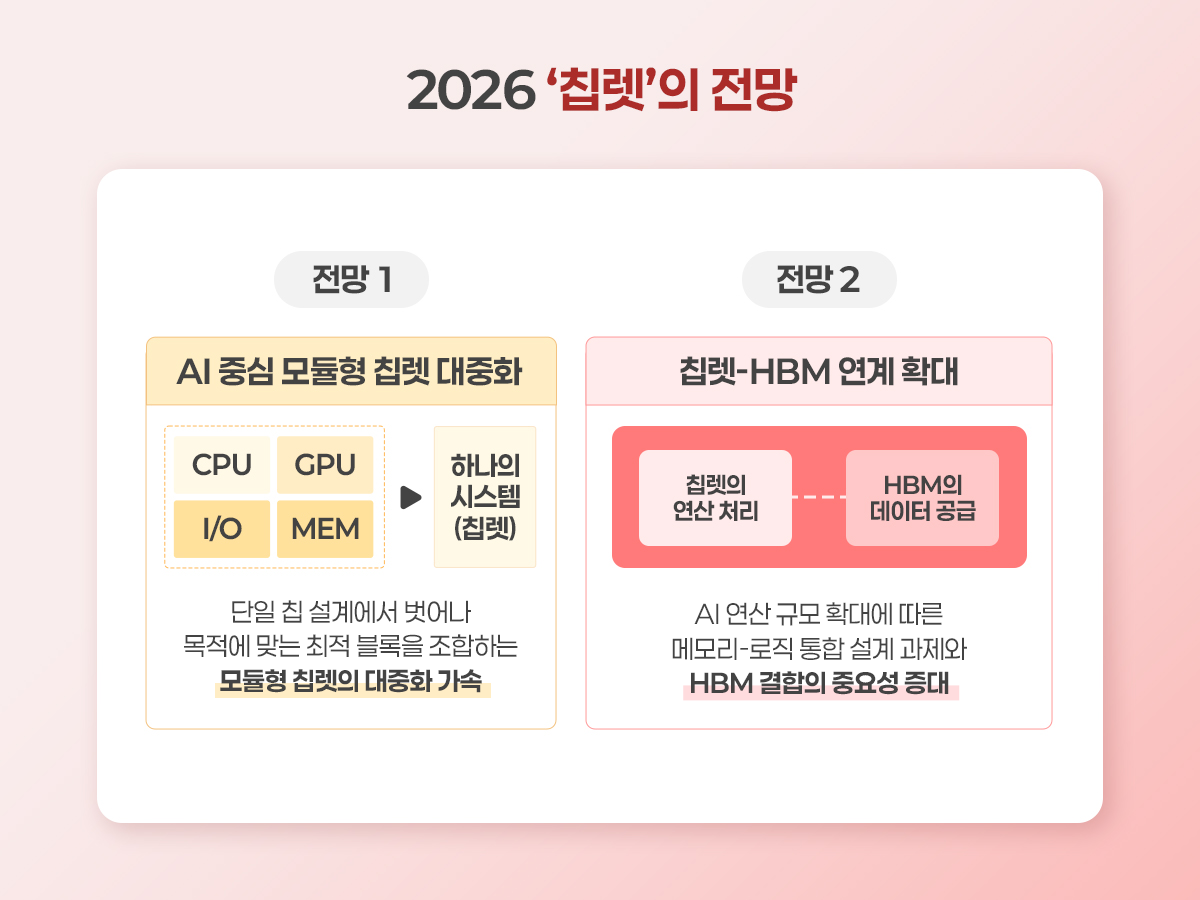

지금까지 칩렛의 개념부터 구조적 특징, 장점까지 살펴봤는데요. 그렇다면 앞으로 칩렛 기술은 어떤 방향으로 발전할까요? 2026년을 기점으로 특히 주목할 만한 두 가지 전망이 있어요.

▪ 전망 1. AI 중심 모듈형 칩렛 대중화

2026년은 단일 칩(Monolithic) 중심의 설계에서 벗어나 목적에 맞는 최적의 블록을 조합하는 시대가 될 전망이에요. 컴퓨팅, 메모리, I/O를 각각 독립된 칩렛으로 제조해 조립하는 방식이 가속화되며, 설계 비용을 절감하고 다양한 공정 노드를 유연하게 혼합해 시장 대응 속도를 획기적으로 높일 수 있게 돼요. 특히 서버·AI 반도체를 중심으로 모듈형 칩렛의 대중화가 빠르게 확산될 것으로 보고 있어요.

▪ 전망 2. 칩렛-HBM 연계 확대

AI 연산 규모가 커질수록 메모리와 로직, 패키징과 전력 관리가 하나의 설계 문제로 묶이고 있어요. 칩렛이 연산 처리를 담당한다면, HBM은 그 연산에 필요한 데이터를 끊임없이 공급하는 역할을 맡아요. 칩렛 방식이 확산될수록 이 둘의 결합은 선택이 아닌 필수가 되는 셈이에요. 반도체 경쟁은 누가 더 빠른 칩을 생산하느냐의 문제가 아니라, 누가 전체 시스템을 예측 가능하게 유지할 수 있느냐의 문제로 이동하고 있어요.

| ➕ 2026 칩렛의 전망 – AI 중심 모듈형 칩렛 대중화 ⠀⠀: 단일 칩 설계에서 벗어나 목적별 최적 블록을 조합하는 모듈형 칩렛 설계의 본격화 전망 – 칩렛-HBM 연계 확대 ⠀⠀: AI 연산 규모 확대에 따른 메모리-로직 통합 설계 과제와 HBM 결합의 중요성 증대 |

지금까지 반도체 설계의 새로운 패러다임, ‘칩렛(Chiplet)’에 대해 자세히 살펴보았어요. 하나의 거대한 칩을 고집하는 대신 잘 만들어진 조각들을 조합하는 칩렛은, 수율·비용·유연성이라는 세 가지 과제를 동시에 해결하며 AI 반도체 시대의 핵심 설계 방식으로 자리잡아 가고 있어요.

그런데 여기서 한 가지 질문이 생겨요. 칩렛으로 ‘연산 성능’을 끌어올렸다면, 그 연산을 쉼 없이 채워줄 ‘데이터 공급’은 어떻게 해결할까요? 아무리 빠른 연산 장치가 있어도, 처리할 데이터가 제때 공급되지 않으면 성능은 절반에 그칠 수밖에 없어요. 바로 이 역할을 맡고 있는 것이 다음 시리즈의 주인공, HBM(고대역폭 메모리)이에요.

[반도체의 모든 것] 다음 편에서는 AI 연산의 ‘데이터 고속도로’, HBM에 대한 더 알찬 이야기로 돌아올게요. 많이 기대해 주세요!

[LX세미콘 소식 바로가기]

⠀

LX세미콘 공식 뉴스룸

LX세미콘 공식 블로그

LX세미콘 공식 유튜브

LX세미콘 공식 페이스북

LX세미콘 공식 인스타그램