지난 두 편의 글에서 실리콘 반도체 소자의 기본 개념과 발전 과정에 대해 함께 알아보았습니다. 이번에는 미래 실리콘 반도체 소자 기술의 핵심인 3차원 반도체 소자 기술에 대해 더 자세히 살펴보도록 하겠습니다. 마치 우리가 사는 도시처럼, 반도체 칩도 이제는 수직으로 올라가는 시대가 왔답니다!

3차원 반도체 소자의 구현 기술과 도전 과제

1. 새로운 차원을 여는 3차원 트랜지스터

여러분은 아파트가 왜 생겼는지 아시나요? 바로 한정된 땅에 더 많은 사람이 살 수 있도록 하기 위해서죠. 반도체 세계에서도 비슷한 일이 일어나고 있습니다. 기존의 2차원 평면 구조로는 더 이상 트랜지스터를 작게 만들기 어려워졌기 때문에, 위로 올라가는 3차원 소자 구조가 등장하게 된 것입니다.

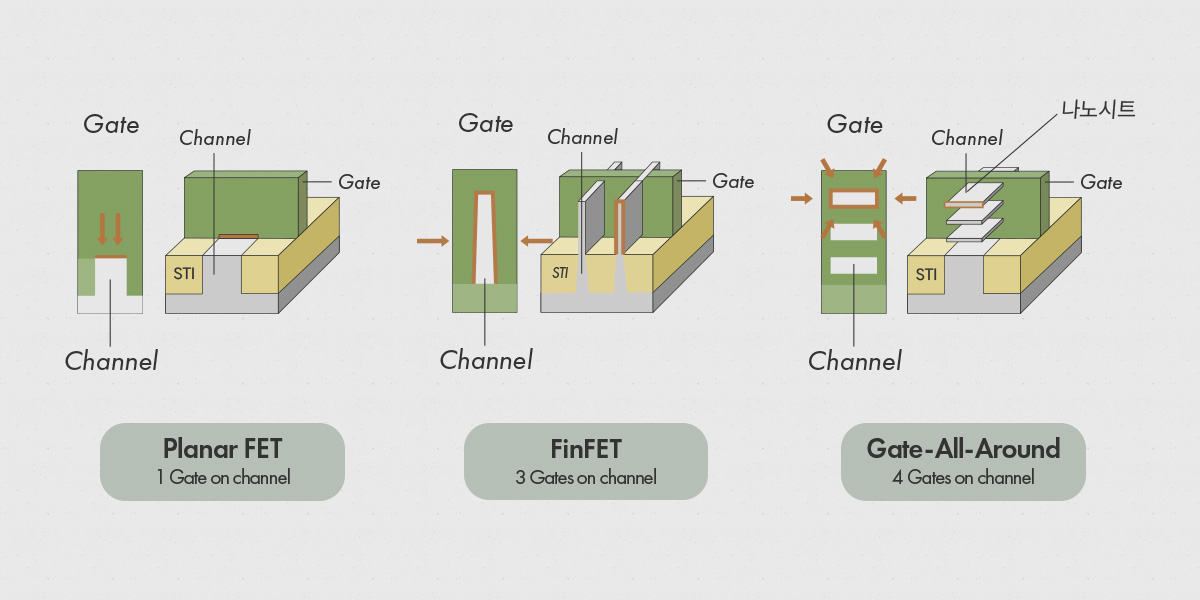

가장 대표적인 3차원 실리콘 트랜지스터 구조는 FinFET입니다. (지난 글에서 다루었는데, 혹시 기억이 잘 안 나면, 다시 지난 글을 참고 해주길 바랍니다.) FinFET의 뒤를 잇는 차세대 3차원 반도체 소자는 바로 “GAA(Gate-All-Around) FET”라는 실리콘 반도체 소자입니다. 이름 그대로 게이트가 채널을 빙 둘러싸고 있는 구조인데요, 마치 소시지를 빵으로 감싼 핫도그처럼 생겼습니다. 이전의 FinFET이 지느러미(Fin) 모양의 채널을 3면에서만 감쌌다면, GAAFET은 채널을 완전히 감싸서 전류의 흐름을 더욱 효과적으로 제어할 수 있습니다. 특히 최신 GAAFET은 여러 개의 나노시트(nanosheet)라는 얇은 채널을 수직으로 쌓은 구조를 가지고 있어요. 마치 여러 층으로 된 아파트처럼요! 각 층(나노시트)마다 게이트가 둘러싸고 있어서, 같은 면적에서 더 많은 전류를 흐르게 할 수 있습니다.

또한 각 나노시트의 폭을 다르게 설계할 수 있어서, 원하는 성능에 맞춰 트랜지스터를 최적화할 수 있다는 장점도 있죠. 이런 구조 덕분에 전력 소비도 줄이고 성능도 높일 수 있게 되었답니다.

그림 1. 반도체 소자 구조의 진화 발전

2. 수직으로 쌓아 올리는 기술

레고 블록을 쌓듯이 반도체 소자로 구성된 반도체 칩들을 위로 쌓는 기술을 “수직 적층 기술”이라고 합니다. 하지만 레고와 달리, 눈에 보이지도 않는 아주 작은 크기의 소자들을 정확하게 쌓아야 하는 어려움이 있습니다. 마치 눈을 감고 천 장의 종이를 똑바로 쌓는 것처럼 어려운 일이죠.

우선, 어떻게 쌓을까요? 수직 적층 기술의 핵심은 “관통전극(TSV: Through-Silicon Via)”이라는 특별한 기술에 있습니다. 이것은 마치 고층 건물의 엘리베이터 통로처럼, 위아래 층을 전기적으로 연결해 주는 통로예요. 머리카락 두께의 수십 분의 일도 안 되는 이 미세한 통로를 정확하게 뚫고, 전기가 잘 통하는 구리 같은 금속으로 채워야 합니다.

이뿐만 아니라, 반도체 칩을 쌓을 때는 쌓는 순서도 매우 중요합니다. 케이크를 만들 때 빵과 크림을 차곡차곡 쌓는 것처럼, 각각의 층이 서로 다른 역할을 하기 때문이죠. 예를 들어, 첫 번째 층에는 정보를 처리하는 시스템 반도체를, 그 위에는 정보를 저장하는 메모리를, 또 그 위에는 외부와 통신하는 센서를 배치하는 식입니다.

그렇다면, 접착제도 필요하다는 생각이 들 것입니다. 각 층을 서로 단단히 붙이기 위해서는 특별한 접합 기술이 필요합니다. 마치 스티커를 붙이듯이, 각 층 사이에 아주 얇은 접착층을 만들어야 해요. 이때 사용되는 접착 물질은 전기가 잘 통하면서도 열에 강해야 하고, 각 층이 서로 떨어지지 않도록 단단히 붙여줘야 합니다.

이렇게 수직으로 칩을 쌓는 과정에서 발생하는 문제들은 어떻게 해결해야 할까요? 이런 어려움을 극복하기 위해 반도체 엔지니어들은 특별한 제작 방법들을 개발했습니다. 예를 들어, 각 층을 만들 때마다 특수한 물질로 표면을 매끈하게 다듬고, 레이저를 이용해 정확한 위치를 확인하는 방법 등을 사용합니다.

하지만, 가장 큰 문제는 열 발생입니다. 여러 층을 쌓다 보면 아래쪽 층에서 발생한 열이 위로 올라가지 못해 문제가 될 수 있어요. 마치 북적이는 지하철역에서 환기가 안 되는 것처럼요. 이를 해결하기 위해 각 층 사이에 아주 작은 방열 통로를 만들거나, 열을 잘 전달하는 특수한 물질을 사용합니다.

또 다른 문제는 층간 신호 간섭입니다. 여러 층의 회로가 서로 가까이 있다 보니, 마치 복잡한 교차로처럼 신호가 뒤섞일 수 있죠. 이를 막기 위해 각 층 사이에 차폐층이라는 특별한 막을 넣어 신호가 섞이지 않도록 합니다.

이러한 모든 과정은 수십 번의 정밀한 공정을 거쳐 이루어지며, 청정실이라는 특수한 공간에서 먼지 한 톨 없이 진행됩니다. 하나라도 잘못되면 전체 칩이 작동하지 않을 수 있기 때문이죠. 그래서 수직 적층 기술은 현대 반도체 기술 중에서도 가장 어려운 기술 중 하나로 꼽힙니다.

차세대 메모리 통합 기술

우리 두뇌는 기억하는 부분과 생각하는 부분이 서로 긴밀하게 연결되어 있습니다. 하지만 지금까지의 컴퓨터는 메모리(기억)와 프로세서(계산)가 물리적으로 떨어져 있어서, 둘 사이를 오가는 데 시간이 많이 걸렸죠. 3차원 구조를 이용하면 메모리와 프로세서를 수직으로 가깝게 배치할 수 있습니다. 마치 1층에 있는 가게와 2층에 있는 창고처럼요. 이렇게 하면 정보를 주고받는 시간이 크게 줄어들어 전체적인 컴퓨팅 성능이 향상됩니다.

최신 그래픽 카드나 인공지능 칩에는 “HBM(High Bandwidth Memory)”이라는 초고속 3차원 메모리가 사용됩니다. HBM은 여러 층의 메모리 칩을 수직으로 쌓고, 이들을 수많은 미세한 연결선으로 이어놓은 구조입니다. 마치 초고층 빌딩의 각 층을 수백 개의 엘리베이터로 연결해 놓은 것과 비슷하죠.

그림 2. 첨단 패키징 기술을 활용한 AI 가속기 구조 (좌측 상단: TSV(관통전극)를 통해 DRAM이 서로 연결된 HBM)

AI시대의 3차원 반도체

인공지능이 발전하면서 더 많은 계산 능력이 필요해지고 있습니다. 3차원 반도체는 이러한 요구를 충족시킬 수 있는 핵심 기술입니다. 특히 뉴런과 비슷한 구조를 가진 뉴로모픽 칩을 3차원으로 구현하면, 훨씬 더 효율적인 AI 처리가 가능해질 것으로 예상됩니다.

향후 10년 동안, 3차원 반도체는 더욱 발전할 것으로 예상됩니다. 100층 이상 쌓은 메모리 칩이 등장하고, 프로세서와 메모리가 하나로 통합된 진정한 3차원 컴퓨터가 만들어질 것으로 보입니다. 3차원 반도체를 만들기 위해서는 새로운 제조 장비와 기술이 필요합니다. 예를 들어, 서로 다른 물질들이 노출된 각 층을 정확하게 연결하기 위한 하이브리드 본딩 (hybrid bonding) 기술이나, 열을 효과적으로 제거하기 위한 냉각 기술 등이 중요해지고 있습니다. 특히, 3차원 구조에서는 열 관리가 매우 중요한데요, 이는 마치 고층 건물에서 환기와 냉난방이 중요한 것과 같은 이치입니다. 이를 위해 특수한 방열 소재를 사용하거나, 미세한 냉각 채널을 만드는 등 다양한 기술이 개발되고 있습니다.

3차원 반도체는 제조 비용이 높다는 단점이 있습니다. 하지만 더 작은 공간에 더 많은 기능을 넣을 수 있고, 전력 효율도 좋기 때문에 장기적으로는 경제적이라고 할 수 있죠. 또한 3차원 반도체 기술은 전 세계 반도체 산업의 지형을 바꿀 수 있는 잠재력을 가지고 있습니다. 이 기술을 먼저 확보하고 대량 생산할 수 있는 기업과 국가가 미래 반도체 시장을 주도하게 될 것입니다.

지금까지 3차원 반도체의 현재와 미래에 대해 알아보았습니다. 비록 아직 해결해야 할 과제들이 많이 있지만, 3차원 반도체는 미래 전자기기의 발전을 이끌 핵심 기술임이 분명합니다. 여러분도 이제 스마트폰이나 컴퓨터를 사용할 때, 그 안에 숨어있는 작지만 놀라운 3차원의 세계를 떠올려보시는 건 어떨까요? 앞으로 더욱 발전할 3차원 반도체 기술이 가져올 미래가 정말 기대되지 않나요?

[LX세미콘 SNS 채널 방문하기]

LX세미콘 블로그 (Semicon人Us)

news.lxsemicon.com

LX세미콘 네이버 포스트

post.naver.com/lxsemiconpr

LX세미콘 유튜브

youtube.com/@LX_Semicon

LX세미콘 페이스북

facebook.com/LXSemicon

LX세미콘 홈페이지

lxsemicon.com